今回はLCRイコライザで使用する可変インダクターについて考察したいと思います。

低域(ターンオーバー側)と高域(ロールオフ側)必要なインダクターのレンジは低域は数百mHから数Hあたり、高域側はおおむね100mH以下のレンジが必要になります。

イコライザの補正を正しく行うためにはL値の精度が良いこと、直流抵抗分が少ないこと、そしてやはり、コストがかからない事が重要です。これらの要件を満たすために、今回のチャレンジではこのインダクタをフェライトコアを使った自作インダクタで賄う方向性に決めました。(ゼネラルトランスのEQ用インダクタもフェライトですね)とはいえ、自作でインダクタをつくったこともないため、本当にうまくできるかどうかの事前検証を行いました。

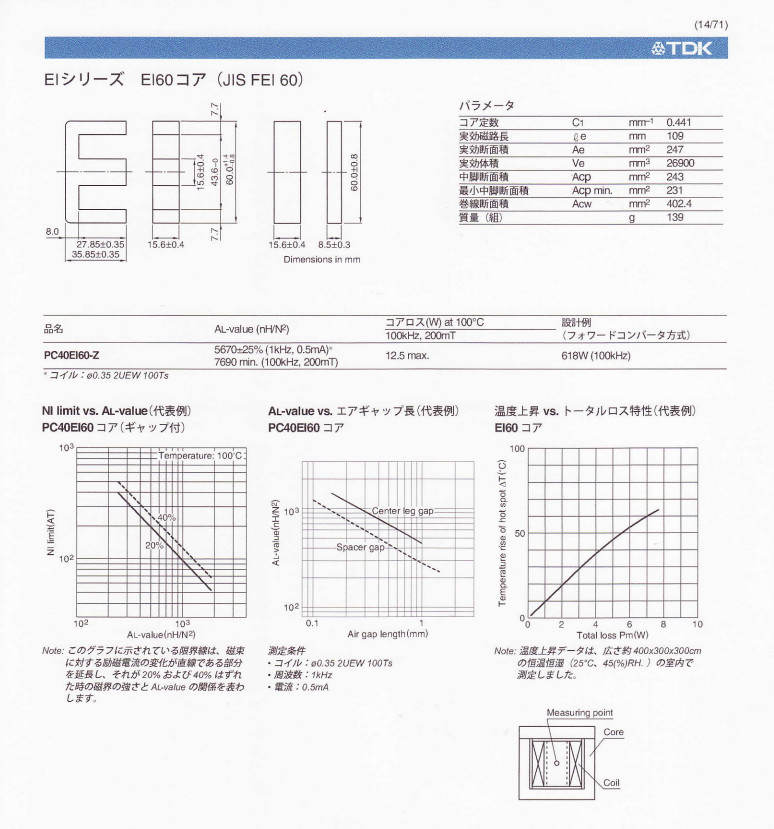

自作のインダクタに使用するコアについては入手がしやすいフェライトコアの中からTDK製のEI-60コア(PC40EI60-Z)を選択しました。コアサイズはEの部分が約60mm*35.85mm*15.6mm(厚)という規格サイズのようです。このコア寸法はゼネラルトランスから出ているEQ用インダクタよりも1回り以上大きなサイズのものです。

規格表を添付します。

ここで

AL Value = 5,670±25%(nH/N^2)

となっているため

L(nH) = AL Value*N^2

= 5,670*N^2

と計算できます。

この値の精度を確認するためにこのコアを使ってUEW線を150ターン巻いてみました。

Lの予想値は

L(H)=5670*150*150×10^(-9)

=0.1275(H)

となりましたが、このインダクタを実測したところEコアとIコアの密着度の度合いによって値が変化する(SETのみ時0.05Hから最大密着で0.1H)ことがわかりました。150回巻きの時、密着度を最大限あげた時にLの予想値である0.1275Hに対して誤差±25%のマイナス側の範囲にギリギリ入ってきたということです。

またEコアとIコア間にギャップを設けた場合のインダクタンスも計測しておきました。

コピー用紙1枚をはさんだ場合

L1(H)=0.043H程度(最大値)まで低下しました。

サランラップ(厚さ11µm)を1層挟んだ場合

L1(H)=0.077H程度(密着度中間にて)となりました。

ギャップ付きコアの場合、ギャップを設けることにより、飽和磁束密度を上昇させることができるとのことですが単位巻き数当たりのインダクタンス値が下がるので、巻き増しが必要となり、その結果として直流抵抗も増加してしまうため落としどころをどこにするか決める必要があります。

今回はギャップはサランラップ1枚厚み(11µm)としました。

この場合のAL値を逆算すると

0.077H=AL*22,500

AL=3,422(nH/N^2)が導き出せます。

各カーブのEQに必要なインダクタンス値の計算は別項に改めて記載しますが、AESカーブ用のターンオーバーが一番大きなL値を必要としていて、その値は約4.43Hです。

これをEI60コアに適合するボビンに巻いたときにどのようになるか、エクセルで計算式をつくり試算してみました。

PC40材料のEI60コアで4.4Hのインダクタンス値を得る場合(サランラップ1層分ギャップ有)

AL=3,422(nH/N^2)から

N^2=4.4/(3,422*10^(-9))=1,285,798

N=1,134回巻き

ボビンの形状は

芯側が17mm*17mm程度、巻き幅25mm程度なので使用するマグネットワイヤをUEWのΦ0.29と設定して概算すると13層完巻き+14層目半分強で必要な巻き数に達します(線長約85m)。層の厚みは約3.5mmとなります。またこの時の直流抵抗値は約22Ωとなり、市販のEQイコライザ用インダクタと比較しても十分低抵抗を達成できることが分かりました、(市販品1.9Hで20-22Ωに対して、自作インダクタは4.4Hで22Ωを予想)

AESカーブに必要なインダクタンス4.43Hが最大値となる為、その途中の値となるRIAA等の別のポジションは、巻き途中で配線を適宜外へ出して端子とすることで全体の配線量を減らそうともくろんでいます。(詳細は設計時)

高域用のロールオフはインダクタンス値も小さい(Maxでも60mH程度)為、こちらはそれぞれ別巻きにしようかと考えています。

本日はここまでとします。

コメント